Arasan Launches xSPI + eMMC Combo PHY IP

Single IP supports both NOR and NAND Flash for embedded systems

Arasan Chip Systems, a leading provider of semiconductor IP for mobile and automobile SoCs, announced the immediate availability of its xSPI + eMMC Combo PHY IP. This IP integrates both the xSPI and eMMC 5.1 PHYs into a single, unified solution, enabling support for two distinct memory protocols within a single IP. The xSPI + eMMC Combo PHY IP is targeted at mission-critical applications in the defence and aerospace industries for SoCs that require the reliability of NOR Flash and the bulk data storage capabilities of NAND Flash, while offering the cost advantages of NAND Flash. This IP can also be used for life-endangering applications like medical devices, wherein reliability is paramount.

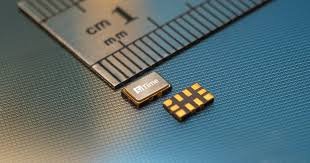

The xSPI + eMMC Combo PHY IP is engineered to address the growing demand for high-performance, area-efficient storage solutions in embedded and boot applications. By leveraging a shared I/O and analogue front-end architecture, the design significantly reduces pin count and silicon footprint, delivering a cost-effective and power-optimised implementation for SoC and MCU platforms.

"This dual-mode PHY allows customers to seamlessly support both eMMC and next-generation xSPI devices with a single low pin count IP, lowering system cost and accelerating time to market. With the launch of our xSPI + eMMC Combo PHY IP , Arasan continues to push the boundaries of storage interface IP innovation," said Ron Mabry, VP of Sales at Arasan.

Arasan offers a comprehensive suite of mobile storage IP for solid state storage interfaces like UFS, eMMC, xSPI, NAND Flash and I2C Controller IP. Arasan has sold over 200 licenses of its eMMC IP and is also the leading provider of xSPI IP, thereby addressing the NOR and NAND Flash markets individually or how with this product, providing a combined solution.